上拉電阻的電壓情況有幾種可能

上拉電阻一般是數字電路和單片機的說法,通常都是以排阻的形式出現。在模擬電路裏這個電阻叫正向偏置電阻。

問題有些含糊,上拉電阻,電壓,幾種可能?

那就從三個部分推測可能

一、工作原理

上拉電阻的目的是給一個正電壓,在數字電路裏表示“1”。除了COMS門電路輸入端不允許懸空,就是單純的給門電路一個可靠的“1”。任何電路都有漏電流,所以當電平信號相互傳遞時就會衰減,而且電壓信號還極易受到幹擾,特別是COMS門電路。而幹擾都是從無到有,即總是以高脈衝出現,所以讓電路可靠動作條件之一就是將低電平作為控製信號,因為幹擾沒有低電平的。所以將電路置“1”就能減小幹擾可能(幹擾了也是1),幹擾信號是電壓很高甚至可以到幾千伏,但沒有電流,可以在給“0” 時被輕易消耗掉,並且沒有足夠的電流抬高電源(電源內阻低會反向耗電)。

MOS電路因為是電壓型控製的,晶體管是電流型的,所以懸空就會很容易受到幹擾,還有靜電損壞。

圖中TTL門電路,發射極就算懸空也不會反轉。COMS門電路太難畫,自己網上看看吧。

模擬電路裏上拉電阻是提供一個靜態工作點。早前數字芯片受技術限製,高阻電阻無法做入芯片,因此需要外置。現在工藝已能滿足,多是通過軟件上拉。

二、工作電壓

單片機常見有3.3V-5V,門電路常見為3.3-5V、±15V等等。

所以上拉電阻的上拉電壓也分幾種。

1、 低壓的,小於5V。

2、 中壓的,小於12V。如繼電器、LED、光耦、PNP三極管等電路的回路電壓。

3、 高壓的,大於12V。這類稱為高閾值門電路,目的就是抗幹擾。因為0與1的中間區分點非常高,在有能耗的環境裏更可靠。這類電路基本都在工業環境中使用,主要是對付強磁場、強電場等電氣噪聲廣泛的環境。

三、上拉電阻的阻值怎麼選

1、後級帶驅動的,需要在不大於芯片允許最大灌電流前提下,滿足後級驅動的最低要求並適當增加裕量,但不宜太大(1.3倍-2倍,否則保護功能容易丟失)。一般這個電流在1-3mA之間。單片機規定,流入的總電流不大於200mA(具體值看芯片手冊)。當單片機強上拉依然不能滿足該驅動電流時,應補足。

2、後級也是芯片的,滿足漏電流即可,多數芯片自帶弱上拉電阻。在存有幹擾的環境依然定為1mA,如5V用5k排阻。

3、一個複雜主板會用到很多上拉電阻,在低電平時會增加能耗,在設計電路時應考慮進去。上拉電阻選型規則:能滿足上拉需求,規格盡量的少,能耗盡量的低。

上拉電阻一般指的是集成電路引腳外部加一個電阻然後接到一個電平吧。上拉電阻的電壓為多少要查看集成電路手冊,看該引腳的耐壓值。有的集成電路引腳不能加超過電源電壓,有的可以。比較典型的是開漏極或開集電極的引腳,上拉電壓可以超過集成電路的電源電壓。

上拉電阻的電壓有幾種可能?在電子電路控製應用中一般是兩種可能,高電平VCC或者是低電平0伏!還是有是在放大電路的應該中,此電壓是在vcc與0伏之間變化的(一般是在1/2vcc範圍變化)!用示波器可以測量到!

|

收音機輸入電壓提高電路要做哪些改動 |

| 首先要明確這個輸入電壓是指信號電壓還是整機工作電壓。 若是信號過強可采用電阻分壓的方式予以衰減,以防大信號阻塞或失真。 如果要提高整機工作電壓,就要看是集成電路還是分立元件。對於集成電路收音機可查一下它的允許工作電壓是多少。比如單片集成電路... |

|

怎麼用數碼管做電壓表 |

| 下麵結合個人經驗和datasheet說一下自己的理解。 1、功能框圖 其實,我也是一個電子行業的新手,打板和元器件選型也沒幹幾年,到今年的六月份也就2年,隻是大學專業是測控,可能基於這點還有些話語優勢。所以,接下來說的、寫的都是個人意見,大神輕噴。 從... |

|

將24v電壓降壓成5v的方法 |

| 應用這塊芯片ADP2441+2個電阻做出的方案,能夠在輸入為4.5-36V的情況下,輸出5V電壓,電流能夠達到1A。 一、目錄: 1、分析需求 2、資料搜集 3、原理分析 4、確定方案 二、正文 1、需求分析: 整個需求,大方向上的要求,隻是需要將24V電壓降低到5V,具體的... |

|

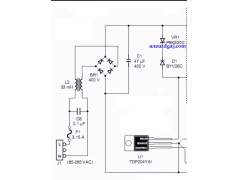

橋式整流輸出155v電壓如何設計 |

| 橋式整流要注意的事項,理論上無非是整流元件和濾波電容的耐壓,以及根據負載的功率大小來決定濾波電容的容量,整流元件的電流的參數。 一個簡單開關電源的輸入部份來講一下。按你問題說的155V直流輸出,可以大概估計出輸入電壓在:155/2即AC110V左右。通過... |

|

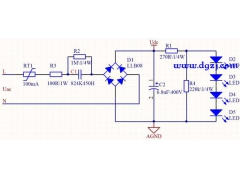

阻容降壓電路輸出電壓的原理講解 |

| 阻容降壓電路結構簡單,成本低廉,它在許多小型的家電中使用非常廣泛,前段時間我維修了一個電熱水壺電路,就使用了一個2.2UF/630V和一個一兆毆的電阻並聯形成了阻容降壓環節。降壓後再經過一個二極管VD半波整流後濾波得到一個12V左右的直流電壓,為後續的低... |